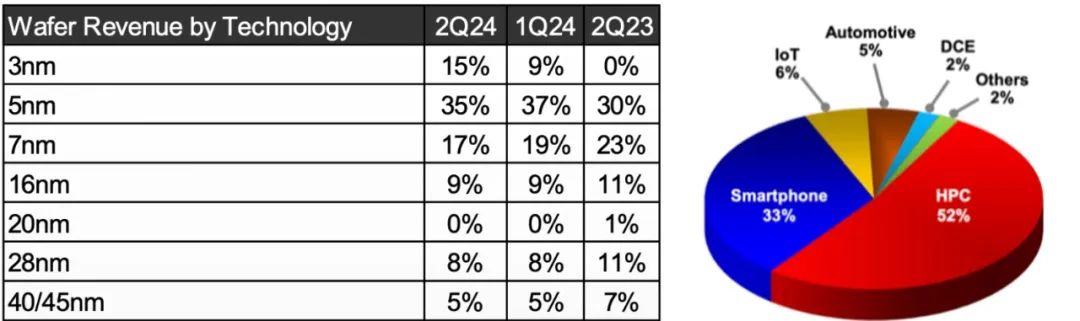

作为半导体产业链中技术壁垒最高的核心环节之一,接口IP(知识产权核)虽占比不大,但已逐步得到国内上下游产业的重视,并实现了快速发展。过去,国内芯片设计长期依赖国外IP厂商,尤其在先进工艺节点领域。近年来,随着国产替代进程加速,国内接口IP产业已逐步突破中低端市场,但在高端接口IP领域仍面临工艺落后、性能指标不足等挑战。当前,全球顶尖晶圆厂的营收重心已向3 nm、5 nm等先进工艺倾斜,而AI、HPC(高性能计算)、自动驾驶等新兴市场对数据带宽、存储效率及低延时的需求爆发,进一步倒逼国产接口IP技术升级。

先进工艺与成熟工艺占比趋势

DDR5技术突围:速度与工艺的双重挑战

DDR5作为新一代内存接口标准,凭借4.8 GT/s至8.4 GT/s的超高速率、更高带宽和更低功耗,成为AI服务器、高性能计算等领域的核心解决方案。然而,其设计复杂度呈指数级增长:信号完整性、功耗控制、高速信号传输等难题,需依托先进工艺实现复杂的模数混合设计,开发周期长、成本高昂。这也导致国内多数芯片企业选择采购第三方成熟的DDR5 IP,而这一市场长期被海外厂商垄断。

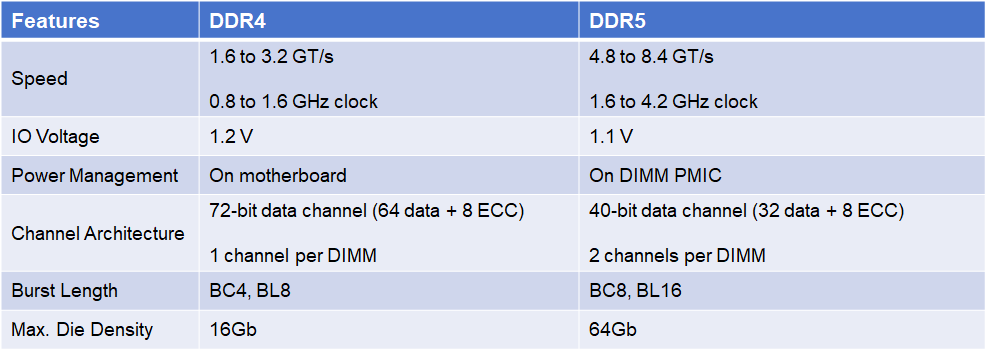

DDR5与DDR4主要差别

牛芯半导体凭借在高速接口领域的技术积累,攻克DDR5/LPDDR5 IP关键技术,其自主研发的“DDR5 MC + PHY IP”完整方案已通过芯片厂商验收,实测速率达8400 Mbps。通过适配国产DDR5颗粒并优化调试方案,该IP在鲁棒性与兼容性上表现突出,为国产高端芯片提供了自主化新选择。

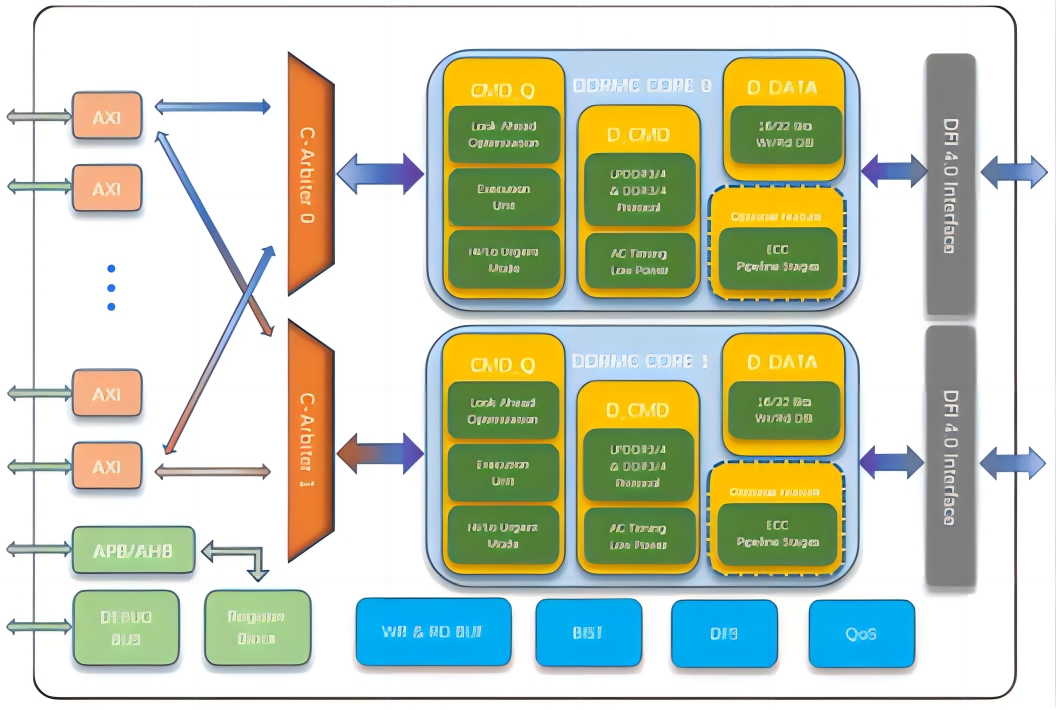

技术特点:从信号完整性到子系统级优化

1、高速信号处理:借鉴SerDes接口的Tx FFE(前馈均衡)和Rx DFE(判决反馈均衡)技术,有效应对信号衰减与码间干扰问题。同时,结合更加精细的实时相位与DCD调整,突破更高速率的限制。

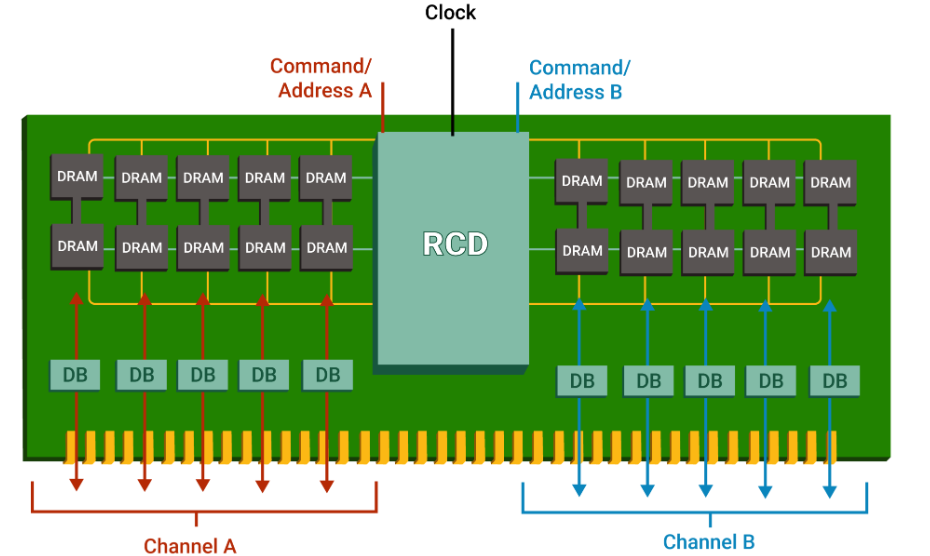

2、两段式训练架构:为应对DDR5 RDIMM/LRDIMM的更高速率、更大容量和更重负载的场景,DDR5 DIMM引入的DB/RCD芯片将传统DDRMC到DRAM颗粒的一段式训练拆分为“DDRMC→DB/RCD”和“DB/RCD→DRAM颗粒”两段式。虽然增加了训练的复杂度,但有效降低了DDR5 PHY信号完整性的压力。

3、低延时、高带宽、低功耗设计:自研DDR5 MC配合DDR5 PHY的子系统,可有效提升整体在低功耗和节能场景下的表现。同时,高效的QoS和Command Queue调度算法,在带宽与时延的性能表现上达到国际一流水准。

DDR5 DIMM方案

本土化优势:定制服务与生态协同

与海外厂商相比,国内IP企业凭借快速响应、深度定制和本地化支持能力,正加速打破垄断格局。牛芯半导体提供从PHY IP、Controller IP到SerDes + DDR一站式解决方案,并可针对客户需求进行链路仿真、信号完整性分析等定制化服务。此外,其IP方案已覆盖国内主流工艺节点,形成“性能 + 性价比”双优势,助力国产SoC向高端应用升级。

牛芯半导体DDR5 IP的突破,标志着国产高端接口IP已进入“技术攻坚 + 生态协同”的新阶段。随着AI、智驾等产业对算力需求的激增,具备自主知识产权的DDR5解决方案将成为国产芯片突围的关键抓手,进一步推动产业链上下游的深度协同与创新。

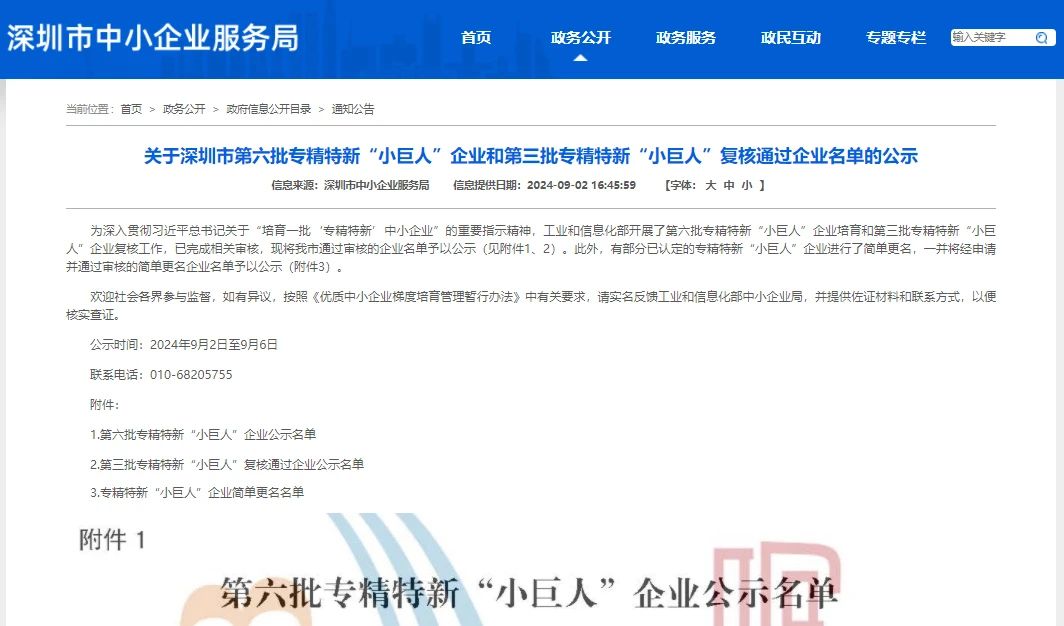

牛芯半导体成立于2020年,聚焦中高端接口IP的开发和授权,并提供相关整体解决方案,致力成为全球领先的IP供应商。牛芯研发人员占比80%以上,其中约80%拥有硕士及以上学历,核心成员具备近二十年的接口IP/芯片开发经验。公司已在深圳、北京、上海、西安设立研发中心,累计申请专利超百项,已授权专利超过70%。凭借硬核技术实力,牛芯半导体相继获评国家级高新技术企业、国家级专精特新“小巨人”企业,并获批广东省接口IP工程技术研究中心等。