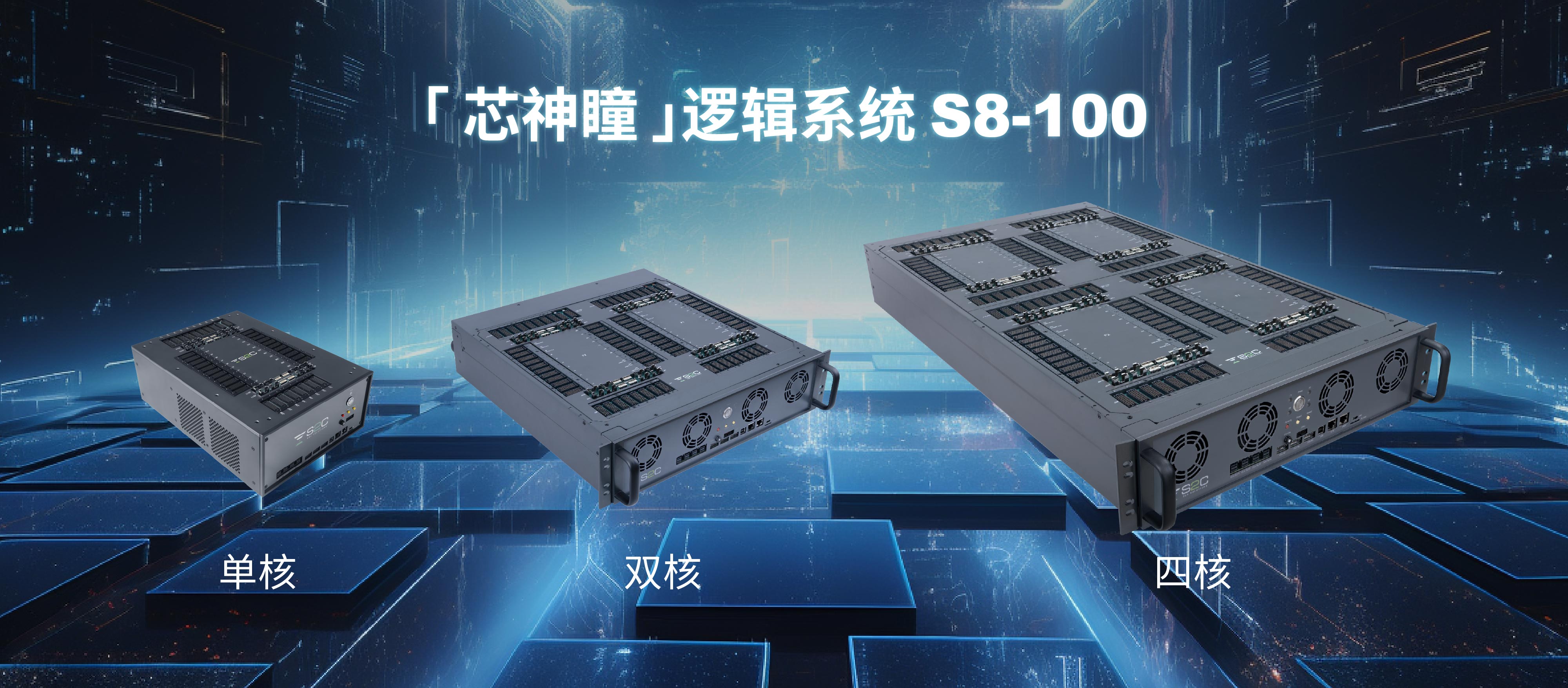

2024年12月19日,国内首家数字EDA供应商思尔芯(S2C)第八代原型验证——芯神瞳逻辑系统S8-100,全系已获国内外头部厂商采用。该系列提供单核、双核及四核配置,旨在满足AI、HPC等领域不同规模的设计需求。S8-100搭载了AMD自适应SoC——Versal™ Premium VP1902,单系统等效逻辑门约1亿门,容量较上代产品提升两倍,支持多系统级联,完美适应超大规模芯片设计需求。此外,该系列还配备全面的工具链,特别是在分割软件上的创新升级,显著提高了原型验证的搭建速度和验证效率。

芯神瞳逻辑系统S8-100的4大优势:

丰富资源与可扩展性:单核支持 18,507K 系统逻辑单元和高达 858Mb 的内部存储,以及 6,864 个 DSP 单元,显著增强逻辑处理能力。可多核组网扩展容量,满足超大规模芯片设计的需求。

高速、灵活的 I/O 架构:最高配备 2,212 个 XPIOs 和多种 GTM/GTYP 收发器,这些 I/O 连接器支持高达 56Gbps 的传输速度和多种高速协议。同时,I/O 电压可动态灵活配置成 1.0V ~ 1.5V,增加了适用性,使其能够适应各种不同的系统需求。

全自动时序驱动分割软件:自动化分割软件经过全面升级,支持TDM aware、多策略PR及智能调度等功能。可以一键实现从RTL到Bitstream自动生成,大幅提高设计和验证效率,缩短开发周期。

完善的工具链:配备PlayerPro自动原型编译软件、ProtoBridge协同仿真软件等完整工具链,大大简化系统性能优化与多核调试。此外还提供了丰富的外置应用库,涵盖主流接口子卡、高速接口降速桥和内存接口转换IP等,加速系统部署,促进软硬件协同开发。

思尔芯S8-100单系统等效逻辑门约1亿门,相较于前代逻辑系统S7-19P,其容量提升了2倍。此外,S8-100的I/O带宽也提升2.5倍,并配备了更灵活、可扩展的I/O架构,轻松应对不同外设与复杂互联拓扑的需求。S8-100透过GTYP支持PCIe Gen5,并提供8个速率高达56Gbps GTM的MCIO接口,带来强大性能和高效体验。以RISC-V应用领域为例,单核S8-100系统就能满足较大RISC-V核的验证,即便是复杂的RISC-V核也无需分割,从而提升高达3-5倍运行频率,使得软件工程师开发更加得心应手。对于AI和HPC等领域的大规模设计,容量的翻倍使得分割数量大幅度减少,显著降低了拓扑结构的复杂性,工程师们能够更加轻松地组网与优化。

此外,思尔芯还提供丰富的外置应用库,包含多种外设接口子卡、降速桥、内存模型等,并且可提供验证就绪的参考设计,简化用户验证环境的部署。为了满足主流应用领域的需求,思尔芯还提供多种灵活的接口方案包括丰富的高速接口降速桥和内存接口转换IP,例如PCIe Gen5 、400G以太网、LPDDR5/DDR5等。S8-100还支持多核FPGA的深度调试,进一步提高了系统部署的速度和效率。

在AI技术飞速发展的今天,思尔芯创始人、董事长兼CEO林俊雄指出:“当前市场迫切需求能够应对大算力与大模型挑战的EDA工具。为此,我们推出的S8-100全系列产品,凭借其更大的容量、强大的性能、高度的灵活性以及便捷的操作性,正为这一需求提供强有力的支撑。某GPU芯片客户原本使用4台LX2逻辑矩阵(32核的VU19P),在S8-100上对标评估后,整体架构简化。新的配置只需要4台S8-100Q(16核VP1902),性能从7MHz提升到10MHz。互联线缆从700+条减少到300+条,大大提升优化效率。”

透过全自动时序驱动分割软件和S8-100搭配,可一键实现从RTL到Bitstream自动生成,解决大设计分割的挑战。此外,S8-100配备了完整的工具链和自动化软件支持,包括实时控制(Player Pro – RunTime),设计调试(Player Pro – DebugTime)和协同仿真(ProtoBridge)等,大幅提升工作效率。

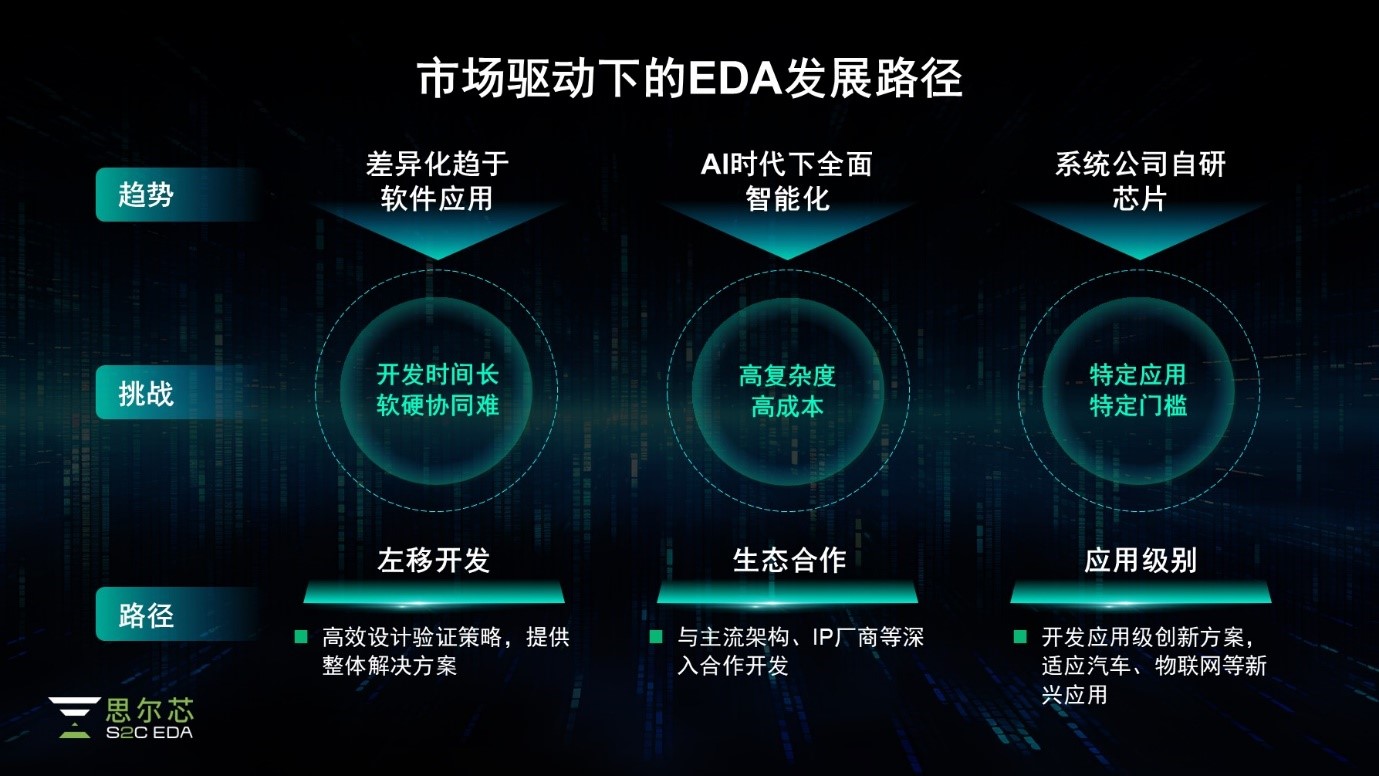

面对不断变化的AI大模型应用场景,思尔芯推出的芯神瞳逻辑系统S8-100全系列,基于公司20余年的技术积累和不断迭代。自成立以来,思尔芯已发布了8代原型验证系统,这些成熟易用的产品经过市场验证,已广泛应用于全球600多家企业。思尔芯始终秉持“以客户为中心、快速响应”的核心价值,产品覆盖从架构设计、软件仿真、硬件仿真到原型验证、数字调试、EDA云等全方位工具和服务,通过完善的数字前端EDA解决方案,为客户提供高效、可靠的支持,助力加速芯片设计创新。