新思科技(Synopsys)披露了1.6纳米背面电源布线项目,这将是万亿晶体管芯片的关键。

新思科技和台积电正在开发支持台积电A16 1.6纳米工艺的背面布线功能,以解决其万亿晶体管设计的电源分配和信号布线问题。

互操作工艺设计工具包(iPDK)和新思科技IC Validator物理验证运行集可供设计团队处理日益复杂的物理验证规则,并高效地将设计过渡到台积电N2 2纳米技术。功率是这些万亿晶体管多芯片设计的关键因素。

联发科(Mediatek)也在台积电使用生产就绪的人工智能驱动EDA流程开发2纳米芯片,台积电、新思科技和Ansys联合开发的支持CoWoS中间层封装的多物理场流程解决了散热和功耗完整性方面的问题。

台积电生态系统与联盟管理部门主管Dan Kochpatcharin表示:“台积电很高兴能与新思科技合作,针对人工智能设计在台积电先进工艺和3DFabric技术上的严格计算需求,开发开创性的EDA和IP解决方案。我们最近在新思科技人工智能驱动的EDA套件和硅验证IP方面的合作成果帮助我们的共同客户显著提高了生产率,并为先进的人工智能芯片设计提供了出色的性能、功耗和面积。”

为了进一步加快芯片设计,新思科技 和台积电通过台积电的云认证,将新思科技EDA工具部署在云端。云认证工具包括综合、放置和路由、静态时序和功耗分析、晶体管级静态时序分析、定制实现、电路仿真、EMIR分析和设计规则检查。

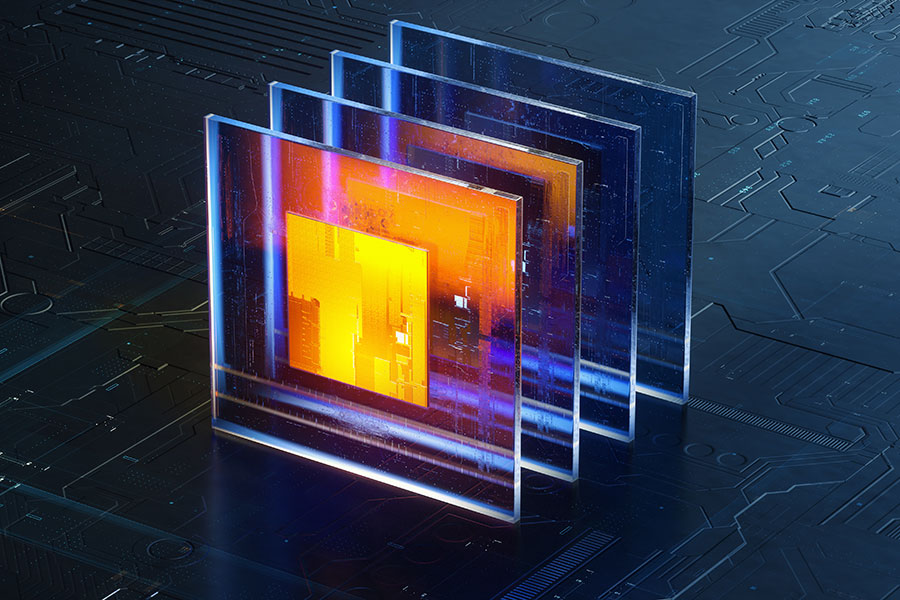

新思科技、Ansys和台积电在多芯片设计中使用了全面系统分析流程,基于新思科技3DIC Compiler统一探索到签核平台。该平台集成了3DSO.ai,与针对数字和3D集成电路的Ansys RedHawk-SC电源完整性签核平台相结合,增强了热分析和红外感知时序分析。新思科技3DIC Compiler是经台积电认证的平台,支持3Dblox、台积电的3DFabric,其中包括台积电的SoIC(系统集成芯片)和CoWoS封装技术。

新思科技采用台积电的CoWoS中间层技术推出了一款测试芯片,全面支持测试、监控、调试和维修功能。通过诊断、可追溯性和任务模式信号完整性监控,可实现设计中、试运行中、生产中和现场优化,以达到预测性维护等目的。用于UCIe PHY的监控、测试和修复 (MTR) IP可在芯片、芯片到芯片接口和多芯片封装层面提供可测试性。

新思科技的UCIe和HBM3 IP解决方案在N3E和N5工艺技术上取得了多项硅成功,加快了IP集成并最大限度地降低了风险。新思科技最新开发的UCIe IP工作速率高达40G,无需增加面积即可实现最大带宽和能效,而HBM4和3DIO IP解决方案则加速了台积电先进工艺上3D堆叠芯片的异构集成。

新思科技目前正在收购Ansys。(校对/李梅)