又到了半导体企业扎堆公布第二季度财报的日子,其中最开心的,一定少不了触底反弹的几家存储芯片厂商。据了解,三星第二季度业绩显著提升,营业利润高达10.44万亿韩元(约合人民币549亿元),同比骤增1462.29%;净利润为9.8413万亿韩元(约合人民币517.7亿元),同比大增470.97%,实现了近14年来最大幅度的净利润增长,而它的韩国友商SK海力士表现同样强劲,第二季度营收增长125%至16.42万亿韩元(约合人民币867亿元)创下历史新高;经营利润环比增长89%至5.47万亿韩元(约合人民币288.8亿元),创2018年二季度以来的最高水平。而此前发布2024财年第三季度财报的美光总营收为68.1亿美元,较上年同期的37.5亿美元同比增长81.6%,远超市场预期。

HBM的架构(来源:AMD东方证券研究所)

三星、SK海力士和美光都公开表示,这场久违的翻身仗的最大“功臣”,就是乘上人工智能高速发展东风的HBM(高带宽存储器),这也坚定了各大存储厂商进一步加大投资,研发下一代HBM的决心。当下,HBM3E是市场主流,但是,行业标准制定组织JEDEC固态技术协会日前发布消息称,HBM4标准即将定稿,新一轮的技术抢位大战也宣告拉开序幕。

HBM4的提升将是一次质的飞跃

当前,AI旺盛的市场需求不断刺激着半导体市场。其中AI服务器对芯片内存容量和传输带宽提出更高要求,拉动了高端存储芯片和高密度存储模组的出货增长,尤其是HBM技术的迭代升级和应用。

据Mordor Intelligence预测,从2024年到2029年,HBM市场规模预计将从约25.2亿美元激增至79.5亿美元,预测期内复合年增长率高达25.86%。为抢占这一增量市场,三星、SK海力士、美光等厂商正在加速推动HBM的规格迭代。

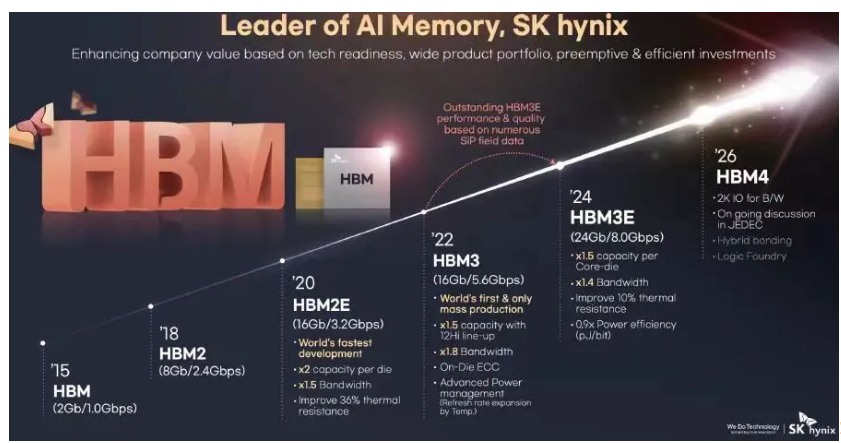

据了解,自2015年HBM技术发布至今,HBM已经从HBM1升级到了HBM3E。每一次技术更新迭代,都会让HBM在带宽、容量、能效、架构以及市场应用等方面取得显著提升。这些提升不仅推动了内存技术的发展和创新,也为高性能计算和人工智能等领域的发展提供了强大的支持。

SK海力士公布的HBM技术路线图(来源:SK海力士)

如今,各大存储厂商积极着手下一代HBM技术——HBM4的研发。根据JEDEC固态技术协会发布的HBM4的初步规范,HBM4将支持每个堆栈2048位接口,数据传输速率高达6.4GT/s,同时还支持更广泛的内存层配置,以更好地应对不同类型的应用需求。新的HBM4标准将包含24GB和32GB层,提供4高、8高、12高和16高TSV(硅通孔)堆栈配置。

TrendForce集邦咨询分析师王豫琪表示,HBM4提高了单个堆栈内的层数,从HBM3的最多12层增加到了最多16层。这一改变对内存的容量和带宽有显著的影响。

对于容量,堆栈层数的增加直接导致了单个HBM4芯片的容量增加。这是因为每一层都可以存储数据,更多的层数意味着更大的总容量。例如,HBM3的单个堆栈最大容量为16Gb,而HBM4则可以达到32Gb。对带宽来说,堆栈层数的增加通常伴随着更多的并行数据通道。HBM4通过将每个堆栈的通道数翻倍,显著提高了并发数据传输的能力。更多的层数还意味着更多的I/O接口,这有助于减少数据传输的延迟,尤其是在多处理器或多GPU系统中,可以更高效地进行数据交换。

此外,还有一个值得注意的关键点是,HBM在所有迭代中都保留了相同的1024位接口,即以相对适中的时钟速度运行的超宽接口。然而,随着内存传输速率要求不断提高,尤其是在DRAM单元的基础物理原理没有改变的情况下,1024位接口已经无法满足未来AI场景的数据传输要求。因此,HBM4需要对高带宽内存技术进行更实质性的改变,也就是升级为更宽的2048位内存接口。

专家表示,接口宽度从1024位增加到2048位会对数据传输性能产生直接的影响,主要体现在以下几个方面。一是带宽增加,接口宽度增加意味着可以传输更大的数据位。1024位接口可以同时发送1024位(即128字节)数据。当接口宽度增加到2048位时,一次传输就可以发送2048位(即256字节)的数据。二是吞吐量提高,如果1024位接口可以在一秒内传输1GB的数据,那么2048位接口在同一秒内理论上可以传输2GB的数据。三是效率提升,特别是在需要大量数据传输的应用中,如高性能计算、图形处理和数据中心服务器等。

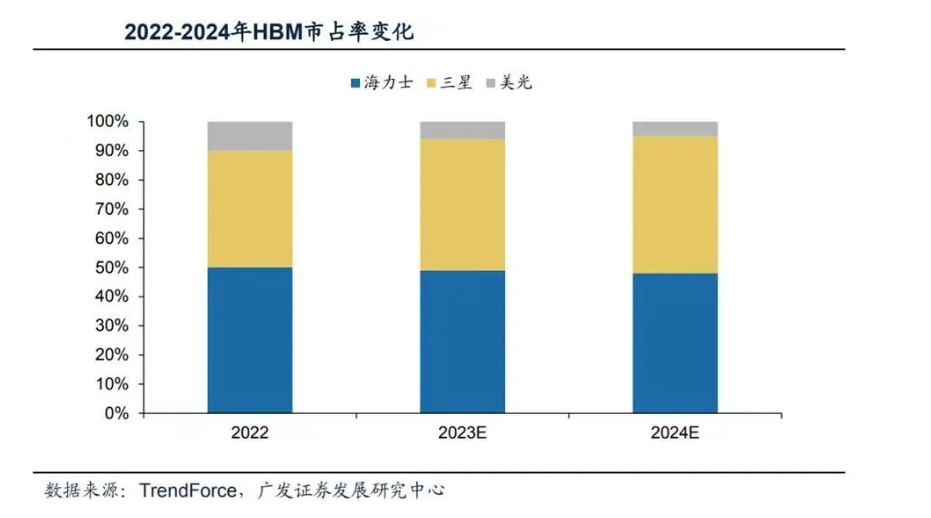

各大企业各显神通抢先机

HBM作为当下存储厂商的兵家必争之地,可谓是得技术者得天下,SK海力士作为HBM技术的先行者,始终保持着技术领先优势,基本在每一代HBM新产品的发布上都压了三星等其他存储厂商一头。市场研究公司TrendForce报告显示,2023年,SK海力士以53%的市场份额领先HBM市场,其次是三星电子的38%和美光的9%。SK海力士更是成为了英伟达的HBM关键供应商。

对于HBM4的市场份额,SK海力士势在必得。

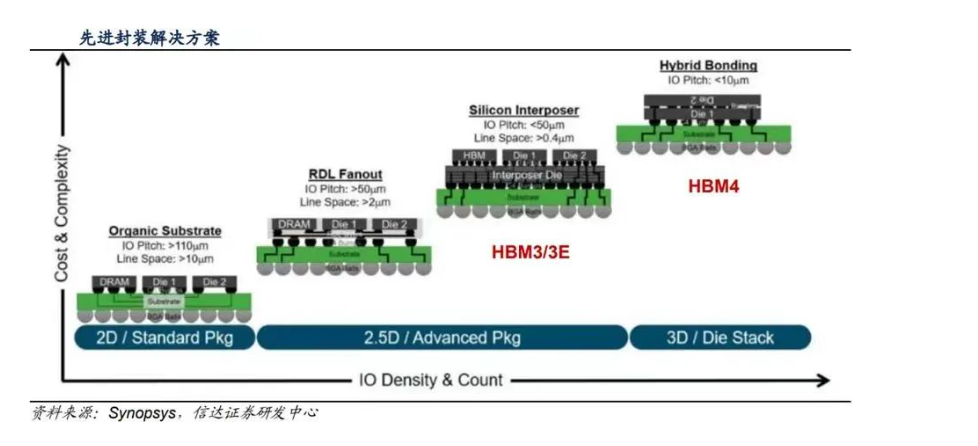

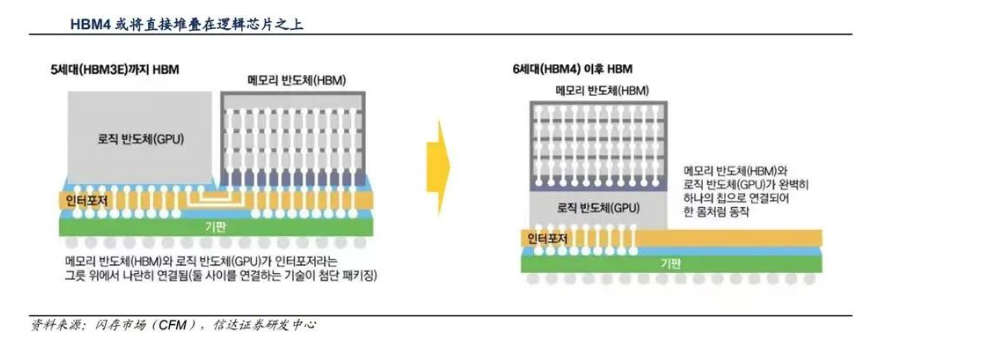

今年4月,SK海力士宣布与台积电签署了一份谅解备忘录,双方将合作生产下一代HBM,并通过先进的封装技术提高逻辑和HBM的集成度。据了解,两家公司将首先对HBM封装内最底层的基础裸片进行性能改善。SK海力士以往的HBM产品都是基于公司自身制程工艺制造基础裸片,但从HBM4产品开始计划采用台积电的先进逻辑工艺。若在基础裸片采用超细微工艺,可以增加更多的功能。由此,公司计划生产在性能和功效等方面更广泛地满足客户需求的定制化HBM产品。SK海力士HBM负责人Kim Gwi-wook表示,SK海力士计划在2025年下半年推出12层DRAM堆叠的首批HBM4产品,于2026年推出16层堆叠的HBM4E产品,内存带宽将是HBM4的1.4倍。产品面市时间将“与英伟达AI加速器发布周期保持一致”。

在上个月,英伟达、台积电和SK海力士三大巨头宣布将组建“三角联盟”,为迎接AI时代共同推进HBM4等下一代技术。可以说,SK海力士目前的势头十分强劲。

而誓要捍卫存储第一大厂地位的三星也不会善罢甘休。对抗台积电和SK海力士的联手,三星需要另辟蹊径,押注自家的4纳米工艺成了关键手段。

据悉,三星原定在HBM4设计采用7纳米工艺,一下子提升到4纳米,固然在芯片性能和用电量方面表现更优秀。但制程研发的花费更高,且良率挑战更大,可以说是一步险棋。

三星一位高管表示:“与台积电和SK海力士不同,芯片设计人员参与HBM4生产是我们的独特优势。”目前,三星已在其设备解决方案部门新设“HBM开发组”,专注于推进HBM4技术。

对于三星的计划,SK海力士和台积电已准备采取相应措施,据了解,两家公司决定在原计划的12纳米制程基础上,增加5纳米制程工艺来生产HBM4。

此外,三星先进封装团队高管Dae Woo Kim在2024年度韩国微电子与封装学会年会上表示,三星成功制造了基于混合键合技术的16层堆叠HBM3内存,该内存样品工作正常,未来16层堆叠混合键合技术将用于HBM4内存量产。

相较现有键合工艺,混合键合无需在DRAM内存层间添加凸块,而是将上下两层直接铜对铜连接,可显著提高信号传输速率,更适合AI计算对高带宽的需求,还可降低DRAM层间距,减少HBM模块整体高度。

面对两大韩国厂商的强势出击,身为美国唯一存储芯片大厂的美光虽然目前的市场占比并不高,却放出豪言,预计2025年,其HBM市占率将与美光的DRAM市占率相当,达到约为20-25%。并且,美光预计将在2026年推出12和16层堆叠的HBM4,带宽超过1.5TB/s;到2027~2028年,还将发布12层和16层堆叠的HBM4E,带宽可达2TB/s以上。

可以预见,各大厂商对于HBM这块大蛋糕的竞争将越来越激烈,我们也有望看到更多的先进技术应用到HBM之中,助力AI攀上新高度。

文章来源:中国电子报

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000