2026年1月,第31届亚洲及南太平洋设计自动化会议(Asia and South Pacific Design Automation Conference, ASP-DAC 2026)在中国香港举行。作为EDA(电子设计自动化)领域的国际重要会议之一,ASP-DAC不仅是展示最新技术成果的舞台,也是学术界与工业界交流的重要平台。

在本届大会上,北京大学集成电路学院EDA团队表现优异,梁云教授团队荣获大会最佳论文奖(Best Paper Award),博士生郭资政荣获学生科研论坛最佳海报奖(SRF Best Poster Award),林亦波副教授团队受邀发表特邀论文并发布了面向工业级设计的异构加速静态时序分析引擎HeteroSTA。 这些成果标志着学院在异构计算辅助芯片设计、高层次综合以及芯片性能分析领域取得了一系列重要进展。相关成果简介如下:

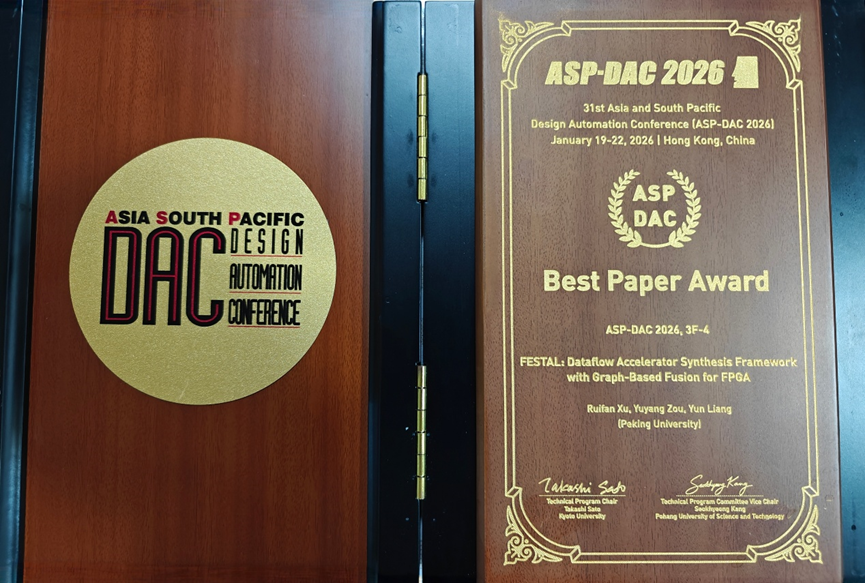

一、 最佳论文奖:基于图融合技术的FPGA数据流加速器综合框架 FESTAL

高层次综合作为一种在软件层级进行硬件设计的方法,极大地提高了设计效率。然而,现有研究大多聚焦于计算层面的优化,往往假设理想的存储系统,导致片上缓存容量有限和片外访存高延迟经常成为制约系统性能的瓶颈。数据流架构虽然能够通过支持任务并行执行和直接片上通信来缓解这一问题,但在实际实现中面临着确定任务间通信模式以及平衡计算与存储资源的重大挑战。目前的综合工具缺乏全面的建模方法,难以充分发挥数据流架构在提升硬件性能方面的潜力。

为解决上述问题,梁云教授研究团队提出了FESTAL,一种基于MLIR的全流程FPGA数据流加速器综合框架。该框架引入了一种新颖的基于图的融合算法,能够系统性地探索任务融合机会,将任务间的通信模式完全优化为片上交互,从而大幅减少了对片外存储的访问需求。通过显式地对存储约束进行建模,FESTAL在计算负载与存储资源之间实现了关键的平衡。实验结果表明,FESTAL在标准测试基准上相比最先进的综合框架实现了平均2.06倍的加速比。在真实应用场景中,FESTAL展现出了与定制化FPGA加速器相当的性能,验证了其在实际部署中的有效性。该工作以《FESTAL: Dataflow Accelerator Synthesis Framework with Graph-Based Fusion for FPGA》为题发表并获会议最佳论文奖,博士生徐瑞帆为第一作者,梁云教授为通讯作者。

二、 学生科研论坛最佳海报奖:异构计算赋能芯片设计优化与验证

在同期举行的学生科研论坛(Student Research Forum, SRF)上,北京大学集成电路学院博士生郭资政(导师林亦波副教授)荣获最佳海报奖(Best Poster Award)。

获奖海报题为《Empowering Chip Design Optimization and Verification with CPU-GPU Heterogeneous Computing》 。该研究工作针对后摩尔时代芯片设计规模激增带来的挑战,系统性地展示了如何利用CPU-GPU异构计算架构突破传统EDA流程的瓶颈:

在验证与分析环节:展示了GPU加速的RTL/门级仿真技术、基于图神经网络(GNN)的早期时序预测模型,以及异构时序签核验证方法 。

在设计优化环节:提出了基于异构计算的可微分时序优化算法,实现了从布局到门尺寸优化的全流程加速 。

相关成果已在DAC、ICCAD等顶级会议发表多篇论文,并多次获得EDA竞赛冠军,通过开源工具和系统性创新,显著提升了芯片设计流程的效率与质量。

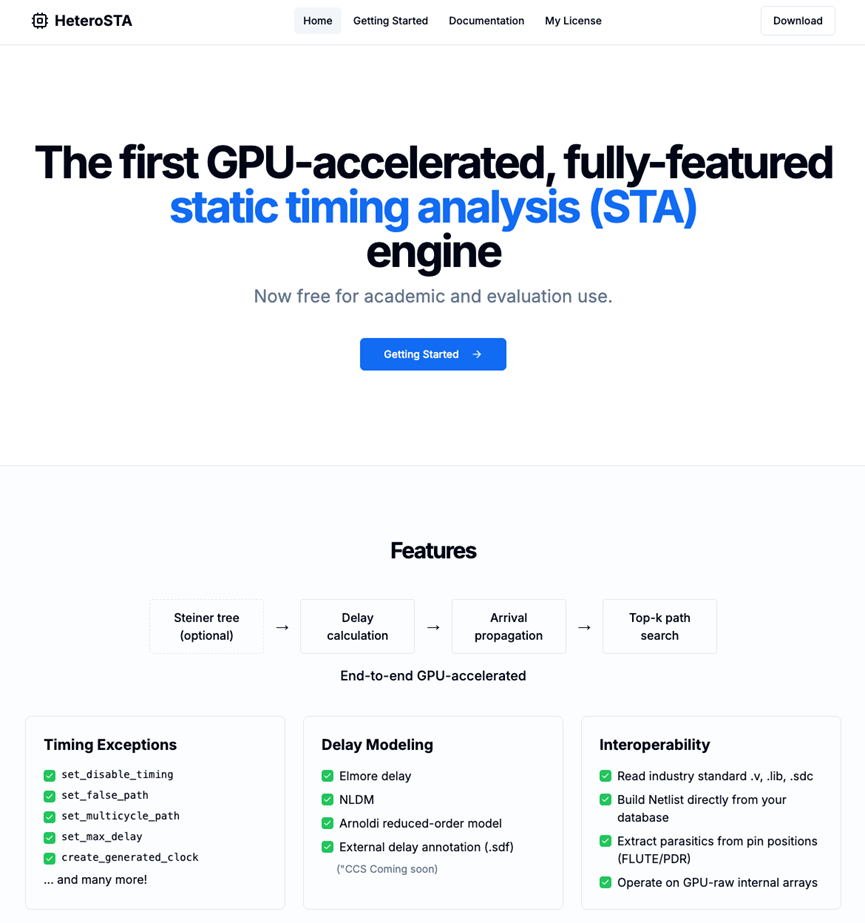

三、 特邀论文与工具发布:工业级异构静态时序分析引擎 HeteroSTA

静态时序分析(STA)贯穿数字电路设计的始终,是决定芯片迭代效率与收敛成本的核心环节 。在本届ASP-DAC上,北京大学集成电路学院林亦波副教授团队发表特邀论文,并发布了异构加速静态时序分析引擎HeteroSTA。

HeteroSTA是业界首款面向工业级设计场景的CPU–GPU异构加速静态时序分析引擎。与传统工具相比,HeteroSTA具备以下核心优势:

10倍加速比:端到端CPU/GPU异构并行加速,覆盖延迟计算、图传播与路径分析,仅需消费级GPU即可达到10倍左右加速比;

高精度延迟:内建多种延迟模型,在速度与精度间灵活权衡,未来还将推出CCS、SI等先进模型;

工业级兼容:完整支持Verilog、Liberty、SPEF、SDC输入,支持各类常见时序例外和层次化设计;

零开销集成:提供动态链接库和C/C++头文件,面向异构计算流程设计的扁平化API,天然适配布局布线、物理优化等优化算法。

HeteroSTA致力于成为下一代异构EDA流程的基础设施,已在时序驱动布局、全局布线、门尺寸调优等真实应用中验证了显著的端到端性能提升。HeteroSTA已在北京大学无锡EDA研究院官网(https://heterosta.pkueda.org.cn/)发布。

该特邀论文题为《HeteroSTA: A CPU-GPU Heterogeneous Static Timing Analysis Engine with Holistic Industrial Design Support》,博士生郭资政为第一作者,林亦波副教授为通讯作者。

关于ASP-DAC

亚洲及南太平洋设计自动化会议(ASP-DAC)是电子设计自动化(EDA)和大规模集成电路(VLSI)设计领域的重要国际会议,与DAC、ICCAD、DATE并称为EDA领域的四大会议。旨在为研究人员、工程师和设计师提供一个展示最新研究成果、探讨技术发展趋势的交流平台。